## 4.5V to 17V Input, 3A Synchronous Step-Down Regulator

### **General Description**

The ET81313 is a highly integrated, wide input voltage, 3A output synchronous buck convertor.

The device is optimized to operate with minimum external component counts and also optimized to achieve low standby current.

This convertor adopts adaptive constant-on-time (ACOT) structure, and provides a fast transient response. It also supports both low-equivalent series resistance (ESR) output capacitors and ultra-low ESR ceramic capacitors with no external compensation components.

During light load operation, ET81313 operates in pulse frequency modulation (PFM) mode, which maintains high efficiency.

ET81313 is available in a SOT-563 package.

#### **Features**

- 3A Converters Integrated  $60m\Omega$  and  $34m\Omega$  FET

- ACOT Mode Control with Fast Transient Response

- Input Voltage Range: 4.5V to 17V

- Output Voltage Range: 0.6V to 7V

- PFM Mode During Light Load Operation

- 1.2MHz Switching Frequency

- Low Shutdown Current Less than 1.6μA(Typ)

- Start-up from Pre-Biased Output Voltage

- Cycle-by-Cycle Over-current Limit

- Hiccup-mode Over-current Protection

- Non-Latch UVP and TSD Protections

- Fixed Soft Start: 1.0ms

- Part No. and Package

| Part No. | Package | MSL    |

|----------|---------|--------|

| ET81313  | SOT-563 | Level1 |

#### **Application**

- Digital TV Power Supply and Surveillance

- Disc Players

- Networking Home Terminal

- Digital Set Top Box

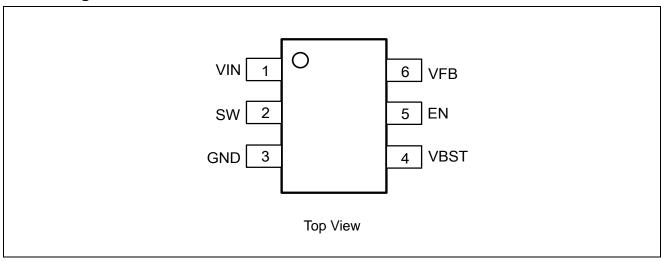

# Pin Configuration

## **Pin Function**

| Pin Name | Pin No. | I/O | Description                                                                                                                               |

|----------|---------|-----|-------------------------------------------------------------------------------------------------------------------------------------------|

| VIN      | 1       | I   | Input voltage supply pin, also the drain terminal of high-side power NFET.                                                                |

| SW       | 2       | 0   | Switch node connection between low-side NFET and high-side NFET.                                                                          |

| GND      | 3       |     | Ground pin of controller circuit, as well as source terminal of low-side power NFET. Connect sensitive VFB to this GND at a single point. |

| VBST     | 4       | 0   | Power supply of high-side NFET control circuit.  Connect 0.1µF capacitor between VBST and SW pins.                                        |

| EN       | 5       | I   | Enable pin. Must be pulled up to enable the device.                                                                                       |

| VFB      | 6       | I   | Output voltage feedback pin. Connect to output voltage with feedback resistor divider.                                                    |

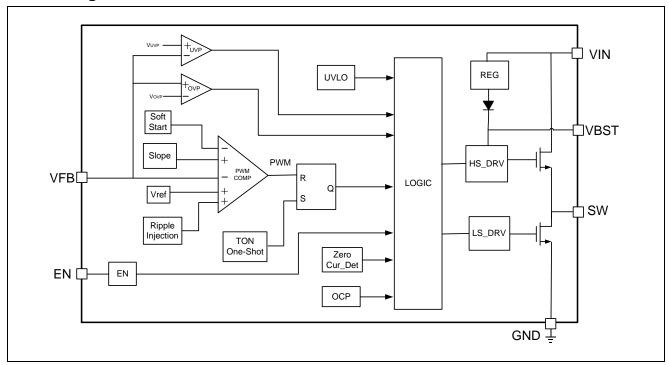

### **Block Diagram**

### **Functional Description**

#### Overview

The ET81313 is highly integrated, 3A synchronous buck converter. It employs adaptive constant on time (ACOT) mode, and supports low ESR output capacitors such as specialty polymer capacitors and multi-layer ceramic capacitors without complex external compensation circuits. The fast transient response of this device can reduce the output capacitance.

#### **Adaptive On-Time Control and PWM Operation**

The main control mode of ET81313 is pulse width modulation (PWM) with ACOT structure. This control mode control can achieve pseudo-fixed frequency and stable operation with both low-ESR and ceramic output capacitors.

The high-side MOSFET is turned on at the beginning of each cycle. When one shot timer expires, the high-side power FET is turned off. This one shot duration is set proportional to input voltage (VIN) and inversely proportional to the output voltage (VO) to achieve pseudo-fixed frequency over the input voltage range, hence it is called adaptive constant on-time control. The one-shot timer is reset and the high-side power FET is turned on again when the feedback voltage falls below the reference voltage. An internal ramp is generated to emulate output ripple, eliminating the need for ESR of output capacitor.

#### **Pulse Frequency modulation**

The ET81313 is designed with pulse frequency modulation mode to achieve high efficiency during light load condition. As the output current decreases from heavy load condition, the inductor current also deceases and eventually comes to zero, which is the boundary between continuous conduction and discontinuous conduction modes. The low-side power FET is turned off when the zero inductor current is detected. As the

load current further decreases the convertor enters into discontinuous conduction mode. The on-time is almost the same as it was in the continuous conduction mode so that it takes longer time to discharge the output capacitor with smaller load current to the level of the reference voltage. This makes the switching frequency lower, proportional to the load current, and keeps efficiency high in light load condition. The transition point to the light load operation  $I_{OUT}(LL)$  current can be calculated in Equation 1.

$$I_{OUT(LL)} = \frac{1}{2 \times L \times f_{sw}} \times \frac{(V_{IN} - V_{OUT}) \times V_{OUT}}{V_{IN}}$$

(1)

In PFM mode, each switching cycle is followed by a period of energy saving sleep time. The sleep time ends when the  $V_{FB}$  voltage falls below the threshold voltage. As the output current decreases, the sleep time between switching pulses increases.

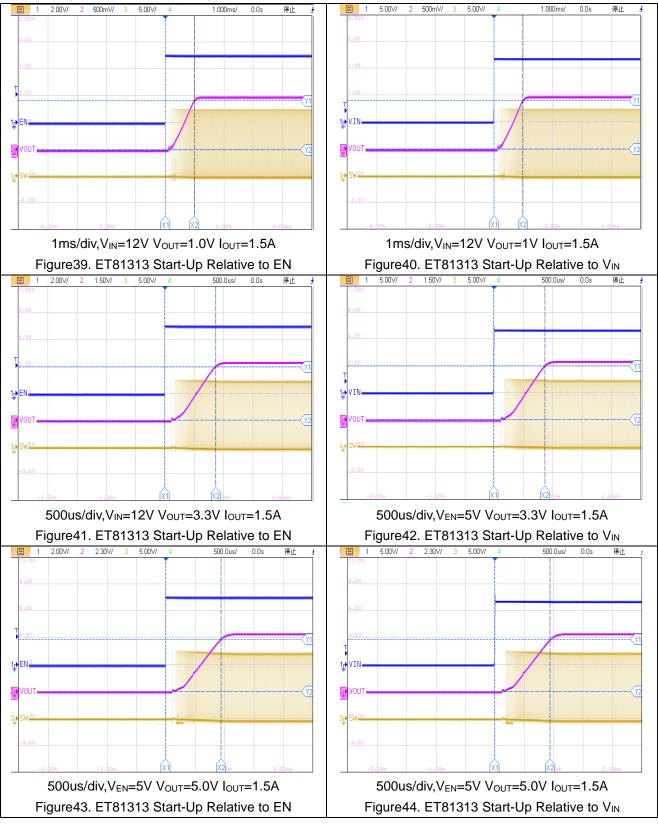

#### Soft Start and Pre-Biased Soft Start

The ET81313 is designed with an internal 1ms soft-start. When the VIN is plugged in and the EN pin becomes high, the reference voltage of PWM comparator begins to rise from zero.

If the output capacitor is pre-biased at start-up, the device begins to switch and start ramping up only after the internal reference voltage becomes greater than the feedback voltage V<sub>FB</sub>. This scheme ensures that the converters ramp up smoothly into regulation point.

#### **Current Protection**

The over-current limit (OCL) is implemented by using cycle-by-cycle valley detect control circuit. The switch current is monitored by measuring the low-side FET drain to source voltage during its on-state. This voltage is proportional to the switch current. To improve accuracy, the voltage sensing is temperature compensated.

During the on-state of high-side FET, the switch current increases at a linear rate determined by  $V_{IN}$ ,  $V_{OUT}$ , and the inductor value. During the on time of the low-side FET switch, this current decreases linearly. The average value of the switch current is the load current  $I_{OUT}$ . If the monitored current is above the OCL level, the converter keeps low-side FET on and prevents the creation of a new set pulse, even the voltage feedback loop requires one, until the current level decreases to OCL level or lower. In next switching cycles, the on-time is set to a fixed value and the current is monitored in the same manner.

The load current is higher than the over-current threshold by one half of the peak-to-peak inductor ripple current. Also, when the current is being limited, the output voltage tends to fall as the load current is higher than the current available from the converter. This may cause the output voltage to fall. When the VFB voltage falls below the UVP threshold voltage, the UVP comparator detects it. And then, the device will shut down after the UVP delay time and re-start after the hiccup time (typically 12ms). When the over current condition is removed, the output voltage returns to the regulated value.

#### **Under-voltage Lockout (UVLO) Protection**

UVLO protection monitors the internal regulator voltage. When the voltage is lower than UVLO threshold voltage, the device is shut off. When input voltage increases up to the upper threshold of UVLO, it begins to switch.

#### **Thermal Shutdown**

The device monitors the temperature of itself. If temperature exceeds the threshold value (typically 170°C), the device is shut off. When the temperature falls to about 140°C or below, the converter begins to switch.

#### **Standby Operation**

When the ET81313 is operating in either normal CCM or PFM, they may be placed in standby by pulling the EN pin to low.

### **Absolute Maximum Ratings**

Over operating free-air temperature range (unless otherwise noted)

|                                                         | Parameters                          | Min  | Max   | Unit |

|---------------------------------------------------------|-------------------------------------|------|-------|------|

|                                                         | VIN, EN                             | -0.3 | 19    | V    |

|                                                         | VBST                                | -0.3 | 24    | V    |

| la a v t                                                | VBST (10ns transient)               | -0.3 | 25    | V    |

| Input                                                   | VBST (VS SW)                        | -0.3 | 6.5   | V    |

| Voltage                                                 | VFB                                 | -0.3 | 6.5   | V    |

|                                                         | SW                                  | -2   | 19    | V    |

|                                                         | SW (10ns transient)                 | -3.5 | 22    | V    |

| Human Body Model (JEDEC JS-001)                         |                                     |      | ±2000 | V    |

| V <sub>ESD</sub>                                        | Charged Device Model (JEDEC JS-002) |      | ±1000 | V    |

| R <sub>θJA</sub> Junction-to-ambient thermal resistance |                                     |      | 135   | °C/W |

| Rejc                                                    | Junction-to-case thermal resistance |      | 45    | °C/W |

| TJ                                                      | Junction Temperature                | -40  | +150  | °C   |

| T <sub>STG</sub>                                        | Storage Temperature                 | -65  | +150  | °C   |

**Note:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum rated conditions for extended periods may affect device reliability.

### **Recommended Operating Conditions**

| Symbol         | Parameters                            |                      | Min  | Max | Unit |

|----------------|---------------------------------------|----------------------|------|-----|------|

| $V_{IN}$       | Supply Inpu                           | it Voltage Range     | 4.5  | 17  |      |

|                |                                       | VBST                 | -0.1 | 22  | V    |

|                |                                       | VBST(10ns transient) | -0.1 | 25  |      |

|                | V <sub>I</sub> Input Voltage<br>Range | VBST (VS SW)         | -0.1 | 6   |      |

| Vı             |                                       | EN                   | -0.1 | 17  |      |

|                |                                       | VFB                  | -0.1 | 5.5 |      |

|                |                                       | SW                   | -1.8 | 17  |      |

|                |                                       | SW(10ns transient)   | -3.5 | 20  |      |

| TJ             | Operating Junction Temperature        |                      | -40  | 125 | °C   |

| T <sub>A</sub> | Ambient Temperature                   |                      | -40  | 85  | °C   |

## **Electrical Characteristics**

$V_{IN} = 12V$ ,  $T_A = -40$ °C to 85°C, (unless otherwise noted)

| Symbol                  | Parameter                                        | Test Conditions                                                  | Min | Тур | Max | Unit |

|-------------------------|--------------------------------------------------|------------------------------------------------------------------|-----|-----|-----|------|

| Supply Curr             | ent                                              |                                                                  |     |     | •   |      |

|                         | Operating-non-switching                          | V <sub>IN</sub> current,                                         |     | 200 |     |      |

| I <sub>IN</sub>         | Supply Current                                   | $V_{EN} = 5V, V_{FB} = 0.8V$                                     |     | 200 |     | μΑ   |

| IINSDN                  | Shutdown supply current                          | V <sub>IN</sub> current, V <sub>EN</sub> = 0V                    |     | 1.6 | 5   |      |

| Logic Thres             | hold                                             |                                                                  |     |     |     |      |

| $V_{ENH}$               | EN High-level Input Voltage                      |                                                                  | 1.2 |     |     | \/   |

| V <sub>ENL</sub>        | EN Low-level Input Voltage                       |                                                                  |     |     | 0.8 | V    |

| Ren                     | EN Pin Resistance to GND                         | V <sub>IN</sub> =12V, V <sub>EN</sub> = 12V                      | 200 | 320 | 600 | kΩ   |

| V <sub>FB</sub> Voltage | and Discharge Resistance                         |                                                                  | •   | •   |     | •    |

| $V_{FBTH}$              | V <sub>FB</sub> Threshold Voltage <sup>(1)</sup> | Vo = 1.05V, Io = 10mA,<br>PFM operation                          |     | 606 |     | mV   |

|                         | V <sub>FB</sub> Threshold Voltage                | Vo = 1.05V, CCM Mode                                             | 580 | 600 | 610 | mV   |

| I <sub>VFB</sub>        | V <sub>FB</sub> Input Current                    | V <sub>IN</sub> =12V, V <sub>FB</sub> = 0.8V                     |     |     | 0.1 | μA   |

| MOSFET                  |                                                  |                                                                  | ı   | ı   |     |      |

| R <sub>DS(on)H</sub>    | High-side Switch Resistance                      | $T_A = 25$ °C, $V_{BST} - V_{SW} = 5V$                           |     | 60  |     | mΩ   |

| R <sub>DS(on)L</sub>    | Low-side Switch Resistance                       | T <sub>A</sub> = 25°C                                            |     | 34  |     | mΩ   |

| Current Limi            | it                                               |                                                                  | ı   | ı   |     |      |

| locu                    | Current Limit                                    | DC current,<br>$V_{OUT} = 1.05V$ , $L_1 = 1.0\mu H$              | 3.5 | 4.8 | 5.5 | А    |

| Thermal Shu             | utdown                                           |                                                                  | ı   | ı   |     |      |

|                         | Thermal Shutdown                                 | Shutdown temperature                                             |     | 170 |     |      |

| T <sub>SDN</sub>        | Threshold (1)                                    | Hysteresis                                                       |     | 30  |     | °C   |

| ON-Time Tin             | ner Control                                      | ·                                                                |     |     | 1   |      |

| toff(MIN)               | Minimum off Time(1)                              | V <sub>FB</sub> = 0.5V                                           |     | 100 |     | ns   |

| Soft Start              |                                                  |                                                                  |     |     | 1   |      |

| tss                     | Soft Start Time(1)                               | Internal soft-start time                                         |     | 1.0 |     | ms   |

| Frequency               | L                                                |                                                                  | ı   | ı   |     |      |

| F <sub>SW</sub>         | Switching Frequency                              | $V_{IN} = 12V$ , $V_O = 3.3V$ , $CCM mode$                       | 1.0 | 1.2 | 1.4 | MHz  |

| Output Unde             | er-voltage and Over-voltage Pr                   | otection                                                         |     |     |     |      |

| V <sub>UVP</sub>        | Output UVP Threshold                             | Hiccup detect (H > L)                                            |     | 60  |     | %    |

| thiccup_wait            | Hiccup on Time                                   |                                                                  |     | 1.4 |     | ms   |

| t <sub>HICCUP_RE</sub>  | Hiccup Time Before Restart                       |                                                                  |     | 8   |     | ms   |

| UVLO                    | -                                                | •                                                                | •   | •   |     | •    |

| UVLU                    |                                                  |                                                                  |     |     |     |      |

| OVLO                    |                                                  | Wake up V <sub>IN</sub> voltage                                  | 3.8 | 4.1 | 4.3 |      |

| V <sub>UVLO</sub>       | UVLO Threshold                                   | Wake up V <sub>IN</sub> voltage Shutdown V <sub>IN</sub> voltage | 3.8 | 4.1 | 4.3 | V    |

6

Note(1). Not production tested, design assurance.

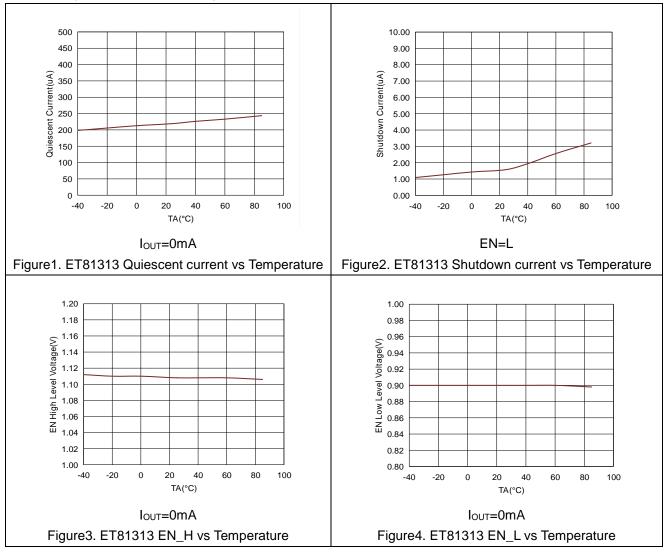

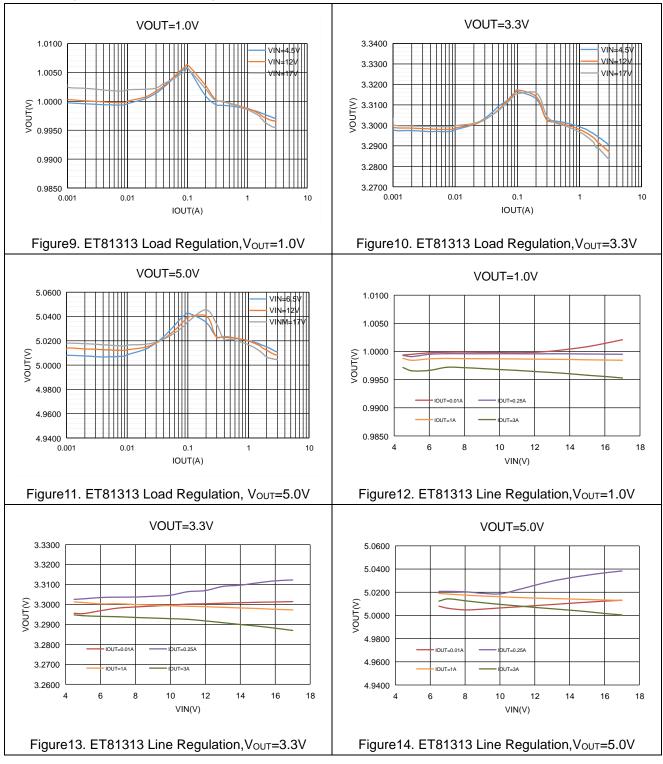

## **Typical Characteristics**

V<sub>IN</sub> = 12V (unless otherwise noted)

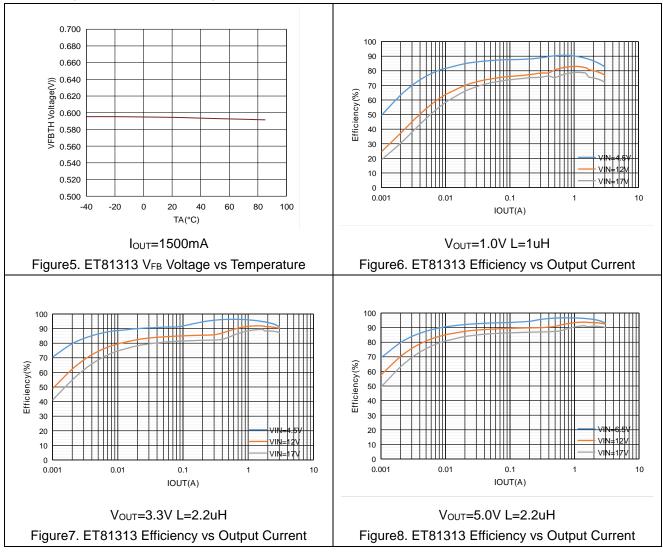

## **Typical Characteristics(Continued)**

$V_{IN} = 12V$  (unless otherwise noted)

### **Application and Implementation**

#### Note

ETEK don't warrant its accuracy or completeness and Information in the following applications sections is not part of the ETEK component specification. Customers should be responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

### **Application Information**

ET81313 is typical step-down DC-DC converter. It's typically used to convert a higher DC voltage to a lower DC voltage with a maximum available output current of 3A. The following design procedure can be used to select component values for the ET81313.

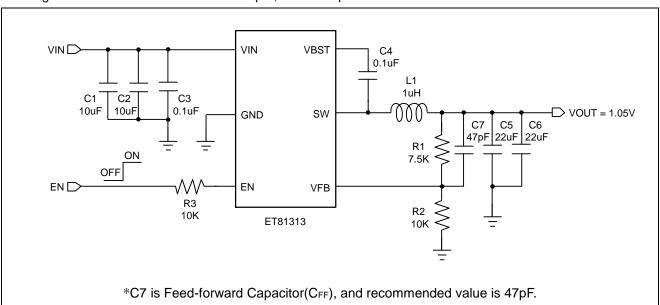

#### **Typical Application**

The application schematic below was developed to meet the previous requirements. This circuit is available as the evaluation module (EVM). The sections provide the design procedure.

The figure shows ET81313 4.5V to 17V input, 1.05V output converter schematics.

V<sub>OUT</sub>=1.05V/3A Reference Design

### **Design Requirements**

This table below shows the design parameters for this application. Table 1.

| Parameter                          | Example Value                 |

|------------------------------------|-------------------------------|

| Input voltage range                | 4.5V to 17V                   |

| Output voltage                     | 1.05V                         |

| Transient response, 1.5A load step | $\Delta V_{OUT} = \pm 3.5 \%$ |

| Input ripple voltage               | 400mV                         |

| Output ripple voltage              | 30mV                          |

| Output current rating              | 3A                            |

| Operating frequency                | 1.2MHz                        |

#### **Detailed Design Procedure**

#### **Output Voltage Resistors Selection**

The output voltage is set with a resistor divider from the output node to the VFB pin. ETEK recommends using 1% tolerance or better divider resistors. Start by using Equation 2 to calculate VOUT.

If customers want to improve efficiency at very light loads, we recommend using larger value resistors. High value of resistor will be more susceptible to noise and voltage errors from the VFB input current will be more noticeable.

$$V_{OUT} = 0.6 \times \left(1 + \frac{R1}{R2}\right) \tag{2}$$

#### **Output Filter Selection**

The LC filter used as the output filter has double pole at:

$$f_{p} = \frac{1}{2\pi \sqrt{L_{OUT} \times C_{OUT}}} \tag{3}$$

The overall loop gain is set by the output set-point resistor divider network and the internal gain of the device at low frequencies. The low frequency phase is 180°. At the output filter pole frequency, the gain rolls off at a -40dB per decade rate and the phase drops rapidly. The inductor and capacitor for the output filter should be selected so that the double pole of Equation 3 is located below the high frequency zero but close enough that the phase boost provided be the high frequency zero provides adequate phase margin for a stable circuit. To meet this requirement use the values recommended in Table 2.

selected so that the double pole of Equation 3 is located below the high frequency zero but close enough that the phase boost provided be the high frequency zero provides adequate phase margin for a stable circuit. To meet this requirement use the values recommended in Table 2.

Table 2. Recommended Component Values

Output R1 R2 L1 ( $\mu$ H) C5 + C6 Voltage (V) ( $\kappa$ Ω) ( $\kappa$ Ω) Min Typ Max ( $\mu$ F)

| Output      | R1    | R2   | L1 (µH) |     |     | C5 + C6       |

|-------------|-------|------|---------|-----|-----|---------------|

| Voltage (V) | (kΩ)  | (kΩ) | Min     | Тур | Max | (μ <b>F</b> ) |

| 1.0         | 6.7   | 10.0 | 1.0     | 1.0 | 4.7 | 20 to 68      |

| 1.05        | 7.5   | 10.0 | 1.0     | 1.0 | 4.7 | 20 to 68      |

| 1.2         | 10    | 10.0 | 1.2     | 1.5 | 4.7 | 20 to 68      |

| 1.5         | 15    | 10.0 | 1.5     | 1.5 | 4.7 | 20 to 68      |

| 1.8         | 20    | 10.0 | 1.5     | 2.2 | 4.7 | 20 to 68      |

| 2.5         | 31.7  | 10.0 | 2.2     | 2.2 | 4.7 | 20 to 68      |

| 3.3         | 45    | 10.0 | 2.2     | 2.2 | 4.7 | 20 to 68      |

| 5.0         | 73.3  | 10.0 | 3.3     | 3.3 | 4.7 | 20 to 68      |

| 6.5         | 98.3  | 10.0 | 3.3     | 3.3 | 4.7 | 20 to 68      |

| 7.0         | 106.7 | 10.0 | 3.3     | 3.3 | 4.7 | 20 to 68      |

The inductor peak-to-peak ripple current, peak current and RMS current are calculated using Equation 4, Equation 5, and Equation 6. The inductor saturation current rating must be greater than the calculated peak current and the RMS or heating current rating must be greater than the calculated RMS current.

$$II_{p-p} = \frac{V_{OUT}}{V_{IN}(MAX)} \times \frac{V_{IN(MAX)} - V_{OUT}}{L_O \times f_{SW}}$$

$$\tag{4}$$

$$II_{peak} = I_O + \frac{II_{p-p}}{2} \tag{5}$$

$$I_{LO(RMS)} = \sqrt{I_O^2 + \frac{1}{12} II_{P-P}^2}$$

(6)

The capacitor value and ESR determines the amount of output voltage ripple. The ET81313 is intended for use with ceramic or other low ESR capacitors. We recommend using values range from 20uF to 68uF. Equation 7 determines the required RMS current rating for the output capacitor

$$I_{CO(RMS)} = \frac{V_{OUT} \times (V_{IN} - V_{OUT})}{\sqrt{12} \times V_{IN} \times L_O \times f_{sw}}$$

(7)

Two  $22\mu F$  output capacitors are used for this design. The typical ESR is  $2m\Omega$  each. The calculated RMS current is 0.286A and each output capacitor is rated for 3A.

#### **Input Capacitor Selection**

The ET81313 requires an input decoupling capacitor and a bulk capacitor is needed depending on the application. We recommend a ceramic capacitor over 10uF for the decoupling capacitor. An additional 0.1uF capacitor (C3) from VIN pin to GND is optional to provide additional high frequency filtering. The capacitor voltage rating needs to be greater than the maximum input voltage.

#### **Bootstrap Capacitor Selection**

A 0.1uF ceramic capacitor must be connected between the VBST to SW pin for proper operation. We recommend using a ceramic capacitor.

#### **Power Supply Recommendations**

ET81313 is designed to operate from input supply voltage in the range of 4.5V to 17V. Buck converters require the input voltage to be higher than the output voltage for proper operation. The maximum recommended operating duty cycle is 75%. Using that criteria, the minimum recommended input voltage is  $V_{OUT}/0.75$ .

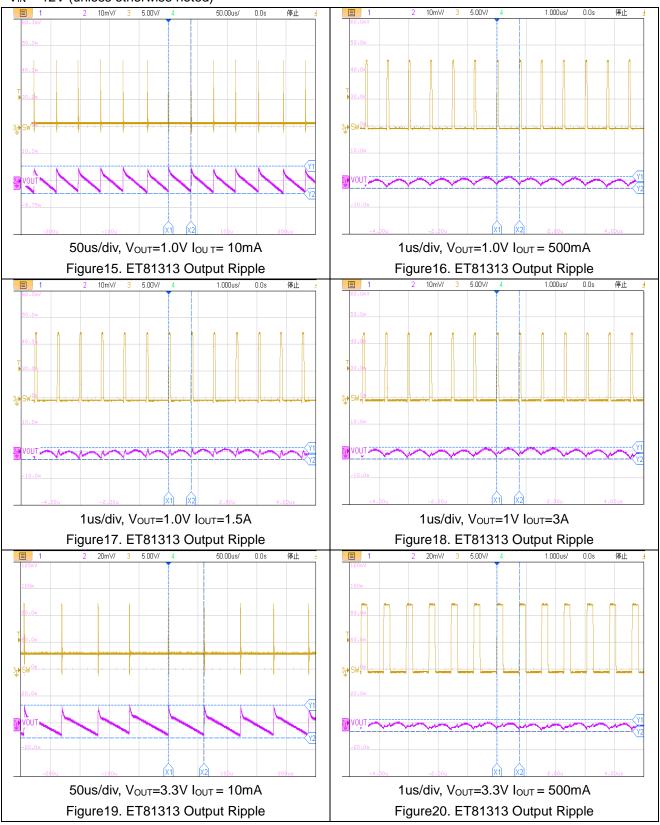

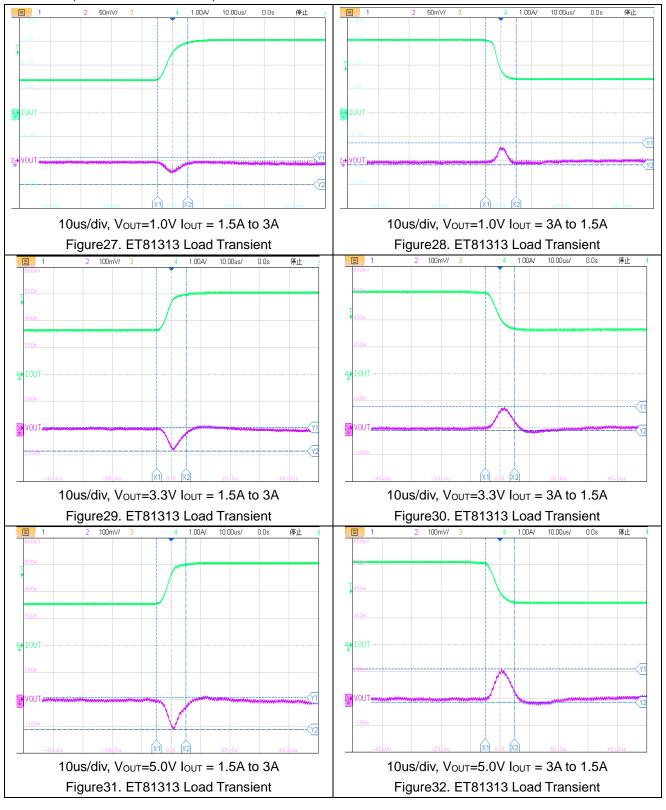

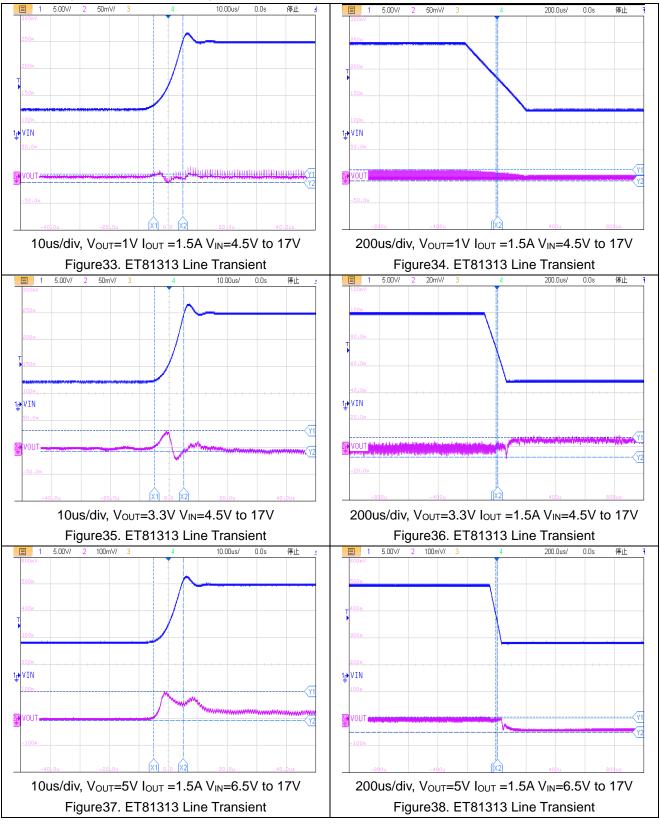

## **Application Curves**

V<sub>IN</sub> = 12V (unless otherwise noted)

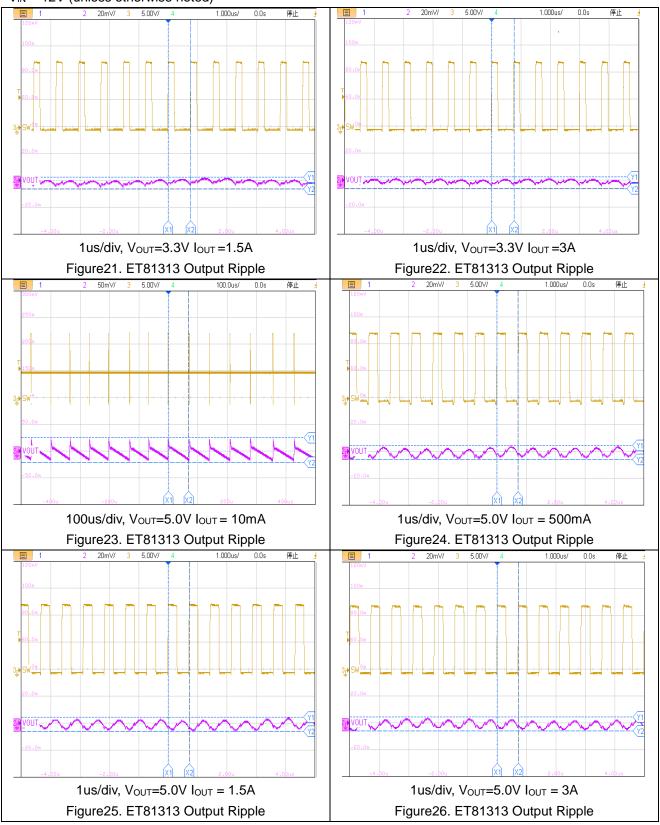

V<sub>IN</sub> = 12V (unless otherwise noted)

V<sub>IN</sub> = 12V (unless otherwise noted)

V<sub>IN</sub> = 12V (unless otherwise noted)

V<sub>IN</sub> = 12V (unless otherwise noted)

$V_{IN} = 12V$  (unless otherwise noted)

### Layout

#### **Layout Guidelines**

- 1. VIN and GND traces should be as wide as possible to reduce trace impedance and better heat dissipation.

- 2. The input capacitor and output capacitor should be placed as close to the device as possible to minimize-trace impedance.

- 3. Provide sufficient Vias for the input capacitor and output capacitor.

- 4. Keep the SW trace physically short and wide to minimize radiated emissions.

- 5. Do not allow switching current to flow under the device.

- 6. A separate VOUT path should be connected to the upper feedback resistor.

- 7. Make a Kelvin connection to the GND pin for the feedback path.

- 8. Voltage feedback loop should be placed away from the high-voltage switching trace, and preferably has ground shield.

- 9. The trace of the VFB node should be as small as possible to avoid noise coupling.

- 10. The GND trace between the output capacitor and the GND pin should be as wide as possible to minimize its-trace impedance.

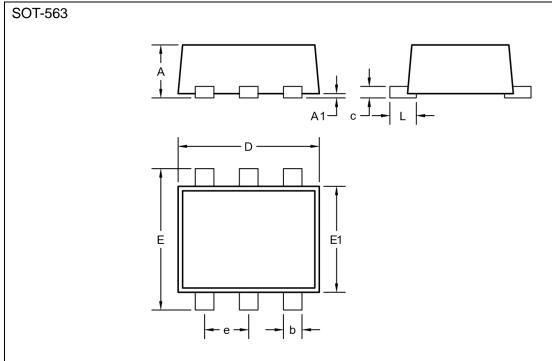

# **Package Dimension**

COMMON DIMENSIONS (UNITS OF MEASURE=MILLIMETER)

| SYMBOL | MIN     | MIN NOM |      |  |

|--------|---------|---------|------|--|

| Α      | 0.525   | _       | 0.6  |  |

| A1     | 0.00    | _       | 0.05 |  |

| b      | 0.17    | 0.22    | 0.27 |  |

| С      | 0.09    | _       | 0.16 |  |

| D      | 1.50    | 1.60    | 1.70 |  |

| Е      | 1.50    | 1.60    | 1.70 |  |

| E1     | 1.10    | 1.20    | 1.30 |  |

| е      | 0.50BSC |         |      |  |

| L      | 0.20    | 0.30    | 0.40 |  |

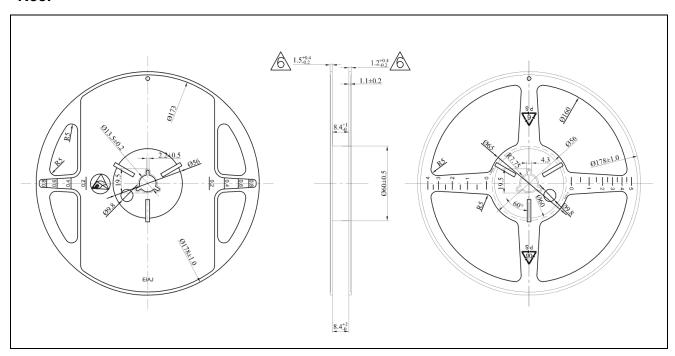

## **Tape Information**

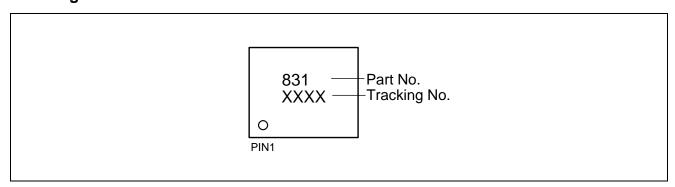

## Marking

### Reel

# **Revision History and Checking Table**

| Version | Date       | Revision Item                                             | Modifier    | Function & Spec<br>Checking | Package & Tape<br>Checking |

|---------|------------|-----------------------------------------------------------|-------------|-----------------------------|----------------------------|

| 0       | 2023-11-31 | Preliminary Version                                       | Xielh Shibo | Xielh                       | Zhujl                      |

| 1.0     | 2024-01-12 | Update Electrical Characteristics                         | Qiuyankang  | Xielh                       | Liujy                      |

| 1.1     | 2024-10-30 | Update Electrical Characteristics and Typical Application | Qiuyankang  | Wuhs                        | Liujy                      |

| 1.2     | 2025-06-18 | Update Marking & Reel                                     | Wuhs        | Xielh                       | Liujy                      |

|         |            |                                                           |             |                             |                            |